Transistor matrix, containing 4 switching epitaxial-planar n-p-n silicon transistors. Designed for use in switching devices

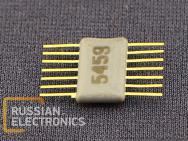

Case type: 401.14-6, metal-ceramic with flexible terminals.

Device type is indicated on its case.

Mass not more than 0.4 g.

Technical requirement version I93.456.000 TU

Technical parameters (at 25 oC)

| Maximum allowed collector constant current, mA | 400 | |

| Maximum allowed collector impulse current, mA | 800 | |

| Maximum collector-to-emitter voltage at given collector current and base-to-emitter resistance, V | 45 | |

| Maximum collector-to-base voltage at given collector current and zero emitter current, V | 45 | |

| Maximum allowed emitter-to-base voltage at zero collector current, V | 4 | |

| Maximum collector power dissipation, W | 0.4 | |

| Static current transfer coefficient | 30..150 | |

| Collector-to-emitter saturation voltage, V | <1 | |

| Collector reverse current, mkA | <6 | |

| Emitter reverse current, mkA | <10 | |

| Beta cutoff, MHz | >200 | |

| Collector junction capacitance, pF | <15 | |

| Emitter junction capacitance, pF | <50 | |

| Maximum junction temperature, oC | 150 | |

| Ambient air temperature, oC | -60..+125 |